FPGA入门 —— DDR3(MIG IP 核) 入门 DDR3 基本内容简介 DDR 简介 DDR=Double Data Rate双倍速率同步动态随机存储器。严格的说DDR应该叫DDR SDRAM,人们习惯称为DDR,其中,SDRAM 是Synchronous Dynamic Random ...

”DDR3 MIG“ 的搜索结果

FPGA开源工作室将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Ar...

本节主要是介绍 Xilinx DDR 控制器 IP 的创建流程、IP 用户使用接口 native 协议介绍和IP 对应的 Example Design 的仿真和上板验证。

利用vivado的MIG控制器来实现DDR3的读写

快速上手Xilinx DDR3 IP核----汇总篇

对于移植别人工程时,需要留意这一点,用两种方式,第一种可以与硬件确认提供的时钟,但是一般这种都是fpga开发者在顶层通过PLL生成的200m时钟 ,另一种方式可以通过旧工程的MIG IP的xdc约束文件去确认下。...

VC707_MIG_DDR3.sim文件夹中是仿真的文件:testbench和DDR3模型参数VC707_MIG_DDR3.srcs文件夹中是源文件,包含DDR3的控制、收发模块、顶层文件

DDR3 MIG IP核

标签: fpga开发

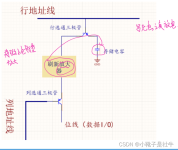

MIG IP 核是 Xilinx 公司针对 DDR 存储器开发的 IP,里面集成存储器控制模块,实现 DDR 读写操作的控制流程,下图是 7 系列的 MIG IP 核结构框图。MIG IP 核对外分出了两组接口。左侧是用户接口,就是用户( FPGA)...

Memory Interface Generator (MIG 7 Series)是 Xilinx 为 7 系列器件提供的 Memory 控制器 IP,使用该 IP 可以很方便地进行 DDR3 的读写操作。本文主要记录 Xilinx DDR3 MIG IP 的仿真过程,包括 IP 配置和 DDR3 ...

近期学习使用Verilog编写DDR3接口的读写测试,在编写过程中遇到许多问题,最终还是功夫不负,实现了DDR3数据写入和数据读取功能。这是完整的工程文件,可以直接进行仿真测试。

DDR3 MIG XILINX FPGA verilog代码,顶层接口封装为fifo,使用简单方便,主要用于大数据量的缓冲,已实际应用在多个项目上

文章结尾包含此专栏文章详细目录。...该专栏包括:MIG的硬件设计讲解,IP底层代码讲解(lut和时钟资源占用,初始化,写入均衡,ZQ校准),app接口和AXIfull接口代码讲解,仿真环境搭建以及讲解,各种DMA示例教程等。

DDR3基本内容介绍 1,DDR3简介 DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据的读取写入是按时钟同步的;所谓动态,是指DDR3中的数据掉电...

Xilinx vivado DDR3 MIG IP核解决方案以及应用

DDR3的相关操作主要包括上电(Power On)、复位(Reset procedrue)、初始化(Initialization)、ZQ对齐(ZQ calibration)、模式寄存器配置(MRS)、自刷新(SR)、刷新(Refreshing)、激活(Activing)、读(Reading)、写(Writing)...

写了简单的DDR3的MIG接口仲裁仿真工程,供初学者学习使用

在vivado中查看某个模块,或者ip所占用的资源,必须run implementation完成,将网表映射到FPGA的物理资源上,通俗点讲,EDA工具将对应...对于时钟资源的使用,bufg使用3个,MMCE使用了1个,Pll使用1个,bufH使用1个。

IP地址表示互联网上的设备的唯一标识,DDR3是一种电脑内存的类型,MIG7则是一个IP核。DDR3 MIG7 IP是一种用来控制DDR3内存的IP核。DDR3内存是一种动态随机存取内存技术,常用于计算机系统,尤其是个人电脑和服务器。...

继上文建立mig ip核后,右键点击生成的IP核,然后选择然后会自动生成一个新工程,点击。

DDR3 MIG是vivado中的DDR3 SDRAM控制器。 DDR3 MIG的脚约束是指对于DDR3 MIG上的各个引脚进行约束设置,以确保其在系统中正常工作。脚约束可以包括时钟信号、数据信号、控制信号等的引脚位置和电气特性。 在进行...

文档介绍了如何将Xilinx DDR3 MIG IP核封装成FIFO接口,以便于在图像处理等场景中存储和处理大量数据。内容包括设计思路、状态机实现、读写FIFO配置、顶层模块连接以及仿真测试。通过封装,简化了读写操作,增加了...

推荐文章

- c语言链表查找成绩不及格,【查找链表面试题】面试问题:C语言学生成绩… - 看准网...-程序员宅基地

- 计算机网络:20 网络应用需求_应用对网络需求-程序员宅基地

- BEVFusion论文解读-程序员宅基地

- multisim怎么设置晶体管rbe_山东大学 模电实验 实验一:单极放大器 - 图文 --程序员宅基地

- 华为OD机试真题-灰度图恢复-2023年OD统一考试(C卷)-程序员宅基地

- 【机器学习】(周志华--西瓜书) 真正例率(TPR)、假正例率(FPR)与查准率(P)、查全率(R)_真正例率和假正例率,查准率,查全率,概念,区别,联系-程序员宅基地

- Python Django 版本对应表以及Mysql对应版本_django版本和mysql对应关系-程序员宅基地

- Maven的pom.xml文件结构之基本配置packaging和多模块聚合结构_pom <packaging>-程序员宅基地

- Composer 原理(二) -- 小丑_composer repositories-程序员宅基地

- W5500+F4官网TCPClient代码出现IP读取有问题,乱码问题_w5500 ping 网络助手 乱码 send(sock_tcps,tcp_server_buff,-程序员宅基地